дјҒдёҡд»Ӣз»Қ

жү¬е·һжіҪж—ӯз”өеӯҗ科жҠҖжңүйҷҗиҙЈд»»е…¬еҸёжҳҜдёҖ家еӨҡе№ҙдё“дёҡд»ҺдәӢеҚҠеҜјдҪ“иҮӘеҠЁеҢ–и®ҫеӨҮз ”еҸ‘дёҺеҲ¶йҖ пјҢйӣҶи®ҫи®ЎгҖҒй”Җе”®гҖҒе®үиЈ…и°ғе·ҘзЁӢж–Ҫе·ҘдёәдёҖдҪ“зҡ„й«ҳжҠҖжңҜдјҒдёҡпјҢз ”еҸ‘жҠҖжңҜдәәе‘ҳеҚ еҲ°е…¬еҸёзҡ„ 50%д»ҘдёҠпјҢз”ҹдә§дәәе‘ҳеҚ 30%пјҢз®ЎзҗҶдәәе‘ҳеҚ 20%гҖӮдёәе®ҢжҲҗжң¬йЎ№зӣ®пјҢжү¬е·һжіҪж—ӯиҒ”еҗҲдёңеҚ—еӨ§еӯҰйӣҶдёӯдәәжүҚдјҳеҠҝпјҢз»„е»әдәҶдёҖж”Ҝд»ҘиҠҰдҝҠеҚҡеЈ«дёәжҠҖжңҜеёҰеӨҙдәәпјҢдёҖжү№й«ҳеӯҰеҺҶгҖҒй«ҳж°ҙе№ізҡ„дёӯйқ’е№ҙеӯҰиҖ…дёәйӘЁе№Ізҡ„еӨҡеӯҰ科дәӨеҸүзҡ„з ”з©¶еӣўйҳҹгҖӮ

зҺ°жңүеӣәе®ҡз ”з©¶дәәе‘ҳ 16 дәәпјҢе…¶дёӯпјҢй«ҳзә§иҒҢз§° 3 дәәпјҢ еІҒд»ҘдёӢдәәе‘ҳеҚ 95пј…д»ҘдёҠпјҢдё“дёҡиғҢжҷҜж¶үеҸҠжңәжў°гҖҒжқҗж–ҷгҖҒжҺ§еҲ¶гҖҒе…үеӯҰгҖҒдҝЎжҒҜзӯүеӨҡеӯҰ科пјҢе…·жңүи®ҫеӨҮз ”еҸ‘гҖҒз”ҹдә§з»ҸйӘҢгҖӮзӣ®еүҚжүҖз ”еҲ¶зҡ„и®ҫеӨҮе·Із»Ҹеә”з”ЁдәҺеҜҢеЈ«йҖҡгҖҒж— й”ЎеҚҺжҷ¶еҫ®з”өеӯҗгҖҒдёӯз”өйӣҶеӣў 55 жүҖз”ҹдә§зәҝгҖӮ

дёҚж–ӯдјҳеҢ–жҠҖжңҜпјҢдҪҝе…¬еҸёи®ҫеӨҮзҡ„жҖ§иғҪжҢҮеҲ°еӣҪеҶ…йўҶе…ҲгҖҒеӣҪйҷ…е…Ҳиҝӣж°ҙе№іпјӣдёҚж–ӯдјҳеҢ–жҲҗжң¬пјҢдҪҝе…¬еҸёзҡ„и®ҫеӨҮдёҺеӣҪеҶ…еӨ–еҗҢиЎҢзӣёжҜ”е…·жңүжҳҺжҳҫзҡ„жҖ§д»·жҜ”дјҳеҠҝпјӣдёҚж–ӯеҠ ејәе“ҒзүҢе»әи®ҫпјҢжҸҗй«ҳжңҚеҠЎиҙЁйҮҸпјҢ并з§ҜжһҒејҖжӢ“жө·еӨ–еёӮеңәпјҢдҪҝзӣ®ж Үдә§е“ҒеңЁеӣҪеҶ…еӨ–е…·жңүзүҢж•Ҳеә”гҖӮйЎ№зӣ®е®ҢжҲҗж—¶пјҢиҫҫеҲ°еӣҪеҶ…еёӮеңәеҚ жңүзҺҮиҫҫ 20пј…д»ҘдёҠпјҢе…¬еҸёе°ҶжҲҗдёәйӣҶжҲҗз”өи·Ҝе°ҒиЈ…жөӢиҜ•и®ҫеӨҮиЎҢдёҡзҡ„йўҶеҶӣдјҒдёҡ

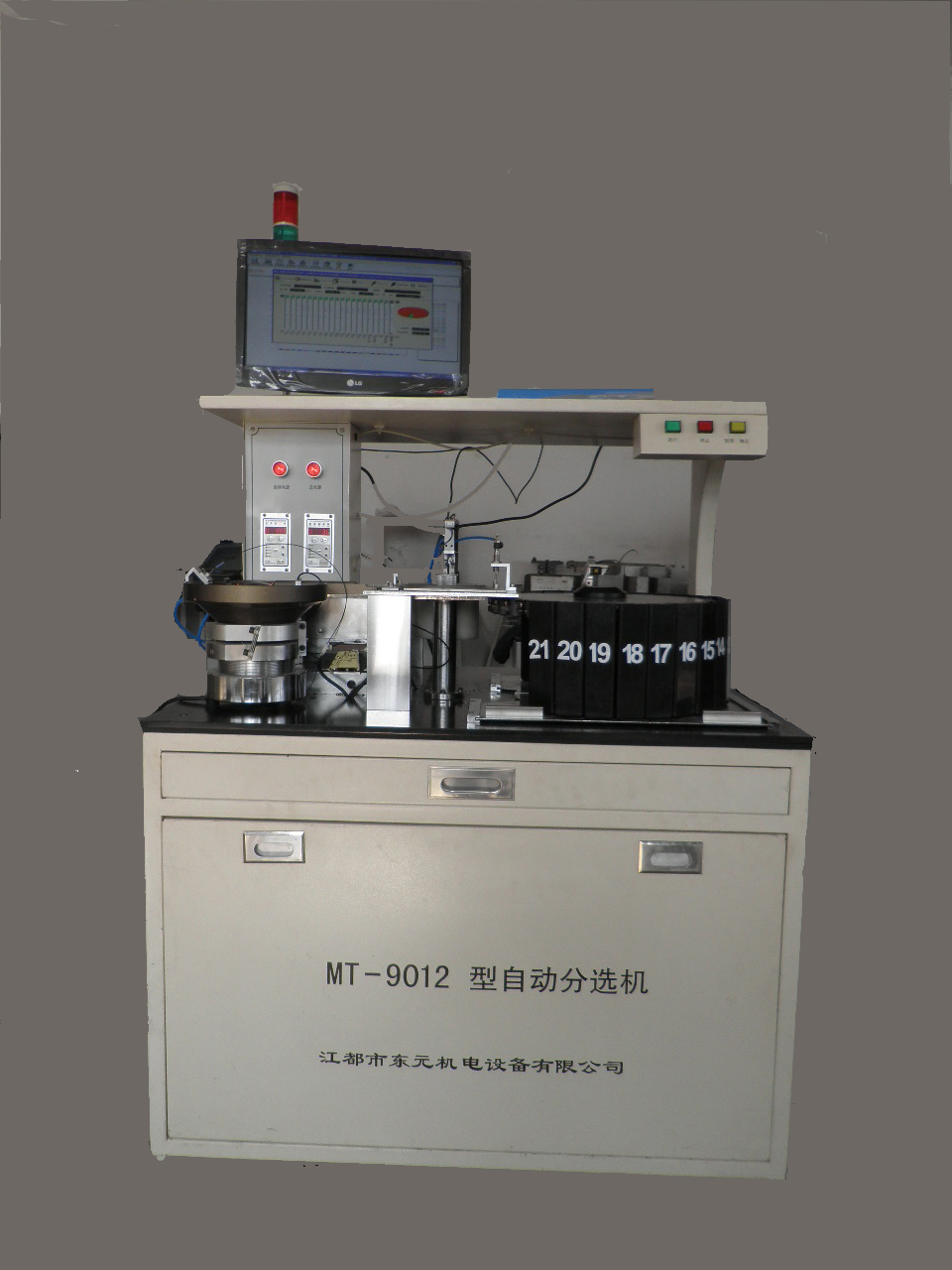

е…¬еҸёдё»иҰҒдёҡеҠЎеҢ…жӢ¬пјҡйӣҶжҲҗз”өи·ҜжЈҖжөӢи®ҫеӨҮгҖҒеҚҠеҜјдҪ“жЈҖжөӢи®ҫеӨҮгҖҒеҚҠеҜјдҪ“еҲҶйҖүи®ҫеӨҮгҖҒеҚҠеҜјдҪ“е°ҒиЈ…и®ҫеӨҮгҖҒеӨӘйҳіиғҪи®ҫеӨҮгҖҒйҷ¶з“·еҲҶйҖүжңәи®ҫеӨҮгҖҒиҮӘеҠЁеҲҶйҖүжңәи®ҫеӨҮгҖӮ

зҺ°жңүеӣәе®ҡз ”з©¶дәәе‘ҳ 16 дәәпјҢе…¶дёӯпјҢй«ҳзә§иҒҢз§° 3 дәәпјҢ еІҒд»ҘдёӢдәәе‘ҳеҚ 95пј…д»ҘдёҠпјҢдё“дёҡиғҢжҷҜж¶үеҸҠжңәжў°гҖҒжқҗж–ҷгҖҒжҺ§еҲ¶гҖҒе…үеӯҰгҖҒдҝЎжҒҜзӯүеӨҡеӯҰ科пјҢе…·жңүи®ҫеӨҮз ”еҸ‘гҖҒз”ҹдә§з»ҸйӘҢгҖӮзӣ®еүҚжүҖз ”еҲ¶зҡ„и®ҫеӨҮе·Із»Ҹеә”з”ЁдәҺеҜҢеЈ«йҖҡгҖҒж— й”ЎеҚҺжҷ¶еҫ®з”өеӯҗгҖҒдёӯз”өйӣҶеӣў 55 жүҖз”ҹдә§зәҝгҖӮ

дёҚж–ӯдјҳеҢ–жҠҖжңҜпјҢдҪҝе…¬еҸёи®ҫеӨҮзҡ„жҖ§иғҪжҢҮеҲ°еӣҪеҶ…йўҶе…ҲгҖҒеӣҪйҷ…е…Ҳиҝӣж°ҙе№іпјӣдёҚж–ӯдјҳеҢ–жҲҗжң¬пјҢдҪҝе…¬еҸёзҡ„и®ҫеӨҮдёҺеӣҪеҶ…еӨ–еҗҢиЎҢзӣёжҜ”е…·жңүжҳҺжҳҫзҡ„жҖ§д»·жҜ”дјҳеҠҝпјӣдёҚж–ӯеҠ ејәе“ҒзүҢе»әи®ҫпјҢжҸҗй«ҳжңҚеҠЎиҙЁйҮҸпјҢ并з§ҜжһҒејҖжӢ“жө·еӨ–еёӮеңәпјҢдҪҝзӣ®ж Үдә§е“ҒеңЁеӣҪеҶ…еӨ–е…·жңүзүҢж•Ҳеә”гҖӮйЎ№зӣ®е®ҢжҲҗж—¶пјҢиҫҫеҲ°еӣҪеҶ…еёӮеңәеҚ жңүзҺҮиҫҫ 20пј…д»ҘдёҠпјҢе…¬еҸёе°ҶжҲҗдёәйӣҶжҲҗз”өи·Ҝе°ҒиЈ…жөӢиҜ•и®ҫеӨҮиЎҢдёҡзҡ„йўҶеҶӣдјҒдёҡ

е…¬еҸёдё»иҰҒдёҡеҠЎеҢ…жӢ¬пјҡйӣҶжҲҗз”өи·ҜжЈҖжөӢи®ҫеӨҮгҖҒеҚҠеҜјдҪ“жЈҖжөӢи®ҫеӨҮгҖҒеҚҠеҜјдҪ“еҲҶйҖүи®ҫеӨҮгҖҒеҚҠеҜјдҪ“е°ҒиЈ…и®ҫеӨҮгҖҒеӨӘйҳіиғҪи®ҫеӨҮгҖҒйҷ¶з“·еҲҶйҖүжңәи®ҫеӨҮгҖҒиҮӘеҠЁеҲҶйҖүжңәи®ҫеӨҮгҖӮ

жүҝжӢ…иҙЈд»»пјҢеӣһжҠҘзӨҫдјҡпјӣдёҚжҮҲиҝҪжұӮпјҢиҮ»дәҺиҮіе–„гҖӮз§үжүҝвҖңеҗҲеҠӣеҗҢиЎҢпјҢеҲӣж–°е…ұиөўвҖқзҡ„дјҒдёҡзҗҶеҝөпјҢиҮҙеҠӣдәҺвҖңе’ҢвҖқж–ҮеҢ–е»әи®ҫпјҢе…¬еҸёе°ҶеҠӘеҠӣжү“йҖ еӣҪеҶ…дёҖжөҒгҖҒжҲҗдёәеӣҪеҶ…йӣҶжҲҗз”өи·ҜжЈҖжөӢи®ҫеӨҮзҡ„йўҶи·‘иҖ…пјҢдәәзұ»ж–ҮжҳҺе’ҢиҝӣжӯҘзҡ„жҺЁеҠЁиҖ…гҖӮ

иҒ”зі»жҲ‘们

ең°еқҖпјҡжү¬е·һеёӮжұҹйғҪеҢәжұҹдҪіи·Ҝ

йӮ®зј–пјҡ225200

з”өиҜқпјҡ0514-86833738

дј зңҹпјҡ0514-86833738

зҪ‘еқҖпјҡdym-handler.com

йӮ®з®ұпјҡzylyb@126.com

йӮ®зј–пјҡ225200

з”өиҜқпјҡ0514-86833738

дј зңҹпјҡ0514-86833738

зҪ‘еқҖпјҡdym-handler.com

йӮ®з®ұпјҡzylyb@126.com